Readout integrated circuit for MIR detector within ASPIC

Paweł Pieńczuk

supervisor: Witold Pleskacz

Under the MIRPIC project, the established consortium (VIGO Photonics, Warsaw University of Technology, Łukasiewicz-IMiF) designs the know-how for Application-Specific Photonic Integrated Circuits (ASPIC) for mid-infrared (MIR, 3-8 um) range. MIR photonics is promising in the field of gas and complex chemical compound sensing. One of the last blocks is the Readout Integrated Circuit (ROIC), which converts the current signal from the MIR detector to the output signal. This ROIC will be integrated within the ASPIC package by the need for miniaturization.

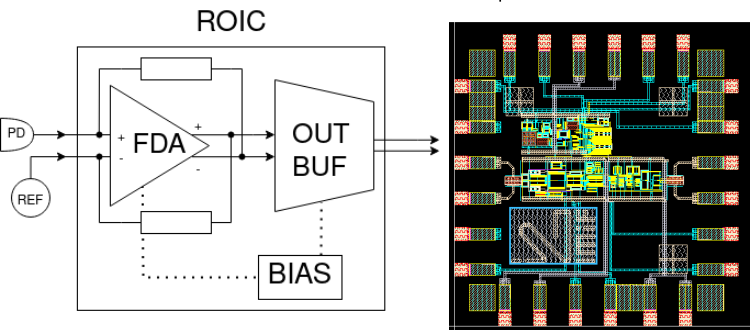

The ROIC (depicted in Fig. 1) unit is based on a transimpedance amplifier (TIA) structure, which converts the input current signal to the output voltage. The TIA is based on a fully differential amplifier (FDA), which can result in high speed and high external noise rejection. The TIA unit is followed by 50 Ohm output buffer (OUT_BUF). Both blocks are polarized by configurable biasing block (BIAS).

Fig. 1 ROIC scheme block (left) and layout (right).

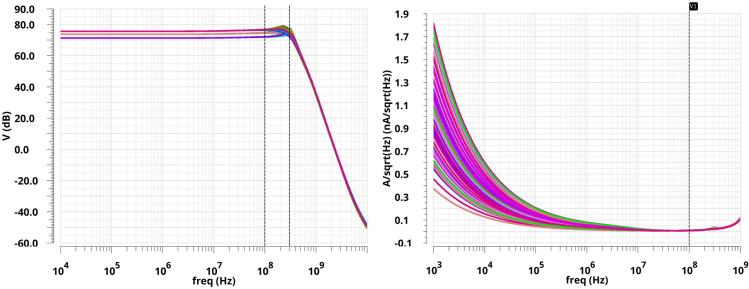

The layout (Fig. 1) is created and sent to production in UMC CMOS 180 nm process. The simulations (Fig. 2) after parasitic extraction show promising results of bandwidth (300 MHz), noise (10 pA/sqrt(Hz) @ 100 MHz), and gain. However, this has to be silicon-proved by experimental tests in the lab.

Fig. 2 ROIC AC (left) and noise (right) characteristics - simulations.

This work has been supported by the National Centre for Research and Development, project "Photonic Integrated Circuits Technologies for mid-IR", MIRPIC, (TECHMATSTRATEG III/0026/2019)