Modelling of Generic Process Design Kit (PDK) Components

for Photonic Integrated Circuits (PICs)

Andrzej Polatynski

supervisor: Ryszard Piramidowicz

Recent developments in versatile Photonic Integrated Circuit (PIC) technologies and hybrid integration processes offer a flexible and cost-efficient way for creating very complex photonic components and integrated circuits for many applications. The fast and efficient test, optimization and verification of new ideas requires an automated and reproducible simulation and design process supporting flexible layout-aware schematic-driven methodologies. When considering very complex designs, even small fabrication tolerances of one building block could make a significant difference in the performance and manufacturability of the whole structure. To reduce the risk of failure and to make performance predictions by virtual prototyping reliable, the simulation model of each single building block needs to be working correctly based not only on the appropriate mathematical and physical equations but also on adequate information provided by the foundry where the final structure will be manufactured.

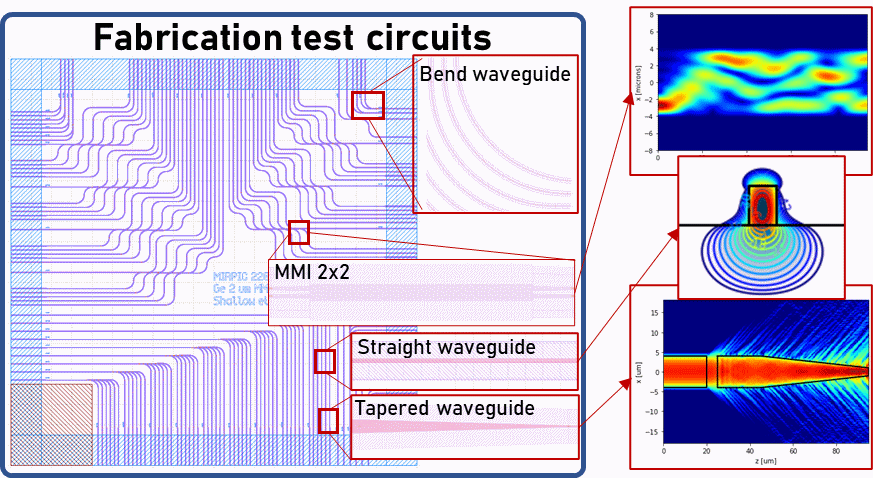

Within the MIRPIC project, we address these design challenges and establish a new versatile integration platform working at the Mid-Infrared wavelength range covering numerous photonics applications in the sensing market. In this poster, I will present our recent platform developments working at the MIR wavelength range (from 3,0 µm to 5,2 µm), including methodologies for modelling and prototyping optical elements and simulation techniques for optimization of crucial parameters. I will demonstrate how the seamless integration between the photonic circuits design tool and foundry knowledge enables the rapid virtual prototyping of complex photonic components and integrated circuits.

Fig. 1 Exemplary test circuit including developed PDK building blocks.

This work received support from the National Centre for Research and Development through MIRPIC project (TECHMATSTRATEG-III/0026/2019-00).